Edition 2.0 2023-09

# INTERNATIONAL IEEE Std 1801™ STANDARD

Delay and power calculation standards – Part 4: Design and Verification of Low-Power, Energy-Aware Electronic Systems

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 25.040.01, 35.060 ISBN 978-2-8322-7540-5

Warning! Make sure that you obtained this publication from an authorized distributor.

### Contents

| 1. Overview                                         |     |

|-----------------------------------------------------|-----|

| 1.1 Scope                                           |     |

| 1.2 Purpose                                         |     |

| 1.3 Key characteristics of the Unified Power Format |     |

| 1.4 Contents of this standard                       | 15  |

| 2. Normative references                             | 16  |

| 2. Political ve Telefenees                          |     |

| 3. Definitions, acronyms, and abbreviations         |     |

| 3.1 Definitions                                     |     |

| 3.2 Acronyms and abbreviations                      | 22  |

| 4. Concepts                                         | 23  |

| 4.1 Introduction                                    |     |

| 4.2 Design structure                                | 24  |

| 4.3 Design representation                           |     |

| 4.4 Power architecture                              |     |

| 4.5 Power distribution.                             |     |

| 4.6 Power management                                |     |

| 4.7 Supply states and power states                  |     |

| 4.8 Simstates                                       |     |

| 4.9 Power intent specification                      |     |

| 5. Language basics                                  | 50  |

| 5.1 UPF is Tcl                                      |     |

| 5.2 Conventions used                                |     |

|                                                     |     |

| 5.3 Lexical elements                                |     |

| 5.4 Boolean expressions                             |     |

| 5.5 Object declaration                              |     |

| 5.6 Attributes of objects                           |     |

| 5.7 Precedence                                      |     |

| 5.8 Generic UPF command semantics                   |     |

| 5.9 effective_element_list semantics                |     |

| 5.10 Command refinement                             |     |

| 5.11 Error handling                                 |     |

| 5.12 Units                                          |     |

| 5.13 SystemC language basic                         | 80  |

| 6. Power intent commands                            | 81  |

| 6.1 Introduction                                    | 81  |

| 6.2 Categories                                      | 81  |

| 6.3 add_parameter                                   | 82  |

| 6.4 add_port_state (legacy)                         | 83  |

| 6.5 add_power_state                                 | 84  |

| 6.6 add_pst_state (legacy)                          | 91  |

| 6.7 add_state_transition                            |     |

| 6.8 add_supply_state                                | 94  |

| 6.9 apply_power_model                               | 95  |

| 6.10 associate_supply_set                           |     |

| 6.11 begin_power_model (legacy)                     | 99  |

| 6.12 bind checker                                   | 100 |

| 6.13 connect_logic_net                       |     |

|----------------------------------------------|-----|

| 6.14 connect_supply_net                      |     |

| 6.15 connect_supply_set                      |     |

| 6.16 create_composite_domain                 |     |

| 6.17 create_hdl2upf_vct                      |     |

| 6.18 create_logic_net                        |     |

| 6.19 create_logic_port                       |     |

| 6.20 create_power_domain                     |     |

| 6.21 create_power_state_group                |     |

| 6.22 create_power_switch                     |     |

| 6.23 create_pst (legacy)                     |     |

| 6.24 create_supply_net                       |     |

| 6.25 create_supply_port                      |     |

| 6.26 create_supply_set                       |     |

| 6.27 create_upf2hdl_vct                      |     |

| 6.28 define_power_model                      |     |

| 6.29 describe_state_transition (deprecated)  | 139 |

| 6.30 end_power_model (legacy)                |     |

| 6.31 find_objects                            |     |

| 6.32 load_simstate_behavior                  |     |

| 6.33 load_upf                                |     |

| 6.34 load_upf_protected (deprecated)         |     |

| 6.35 map_power_switch                        |     |

| 6.36 map_repeater_cell                       |     |

| 6.37 map_retention_cell                      |     |

| 6.38 name_format                             |     |

| 6.39 save_upf                                |     |

| 6.40 set_correlated                          |     |

| 6.41 set_design_attributes                   |     |

| 6.42 set_design_top                          |     |

| 6.43 set_domain_supply_net (legacy)          |     |

| 6.44 set_equivalent                          |     |

| 6.45 set_isolation                           |     |

| 6.46 set_level_shifter                       |     |

| 6.47 set_partial_on_translation              |     |

| 6.48 set_port_attributes                     |     |

| 6.49 set_repeater                            |     |

| 6.50 set_retention                           |     |

| 6.51 set_retention_elements                  |     |

| 6.52 set_scope                               |     |

| 6.53 set_simstate_behavior                   |     |

| 6.54 set_variation                           |     |

| 6.55 sim_assertion_control                   |     |

| 6.56 sim_corruption_control                  |     |

| 6.57 sim_replay_control                      |     |

| 6.58 upf_version                             |     |

| 6.59 use_interface_cell                      | 203 |

|                                              |     |

| 7. Power-management cell definition commands |     |

| 7.1 Introduction                             |     |

| 7.2 define_always_on_cell                    |     |

| 7.3 define_diode_clamp                       |     |

| 7.4 define_isolation_cell                    |     |

| 7.5 define_level_shifter_cell                |     |

| 7.6 define_power_switch_cell                 |     |

| 7.7 define_retention_cell                    | 218 |

| 8. UPF processing                                                          | 220 |

|----------------------------------------------------------------------------|-----|

| 8.1 Overview                                                               | 220 |

| 8.2 Data requirements                                                      | 221 |

| 8.3 Processing phases                                                      | 221 |

| 8.4 Error checking                                                         | 225 |

| 9. Simulation semantics                                                    | 225 |

| 9.1 Supply network creation                                                |     |

| 9.2 Supply network simulation                                              |     |

| 9.3 Power state simulation                                                 |     |

| 9.4 Power state transition detection.                                      |     |

| 9.5 Simstate simulation.                                                   |     |

| 9.6 Transitioning from one simstate state to another                       |     |

| 9.7 Simulation of retention                                                |     |

| 9.8 Simulation of isolation.                                               |     |

| 9.9 Simulation of level-shifting                                           |     |

| 9.10 Simulation of repeaters                                               |     |

| ·                                                                          |     |

| 10. UPF information model                                                  |     |

| 10.1 Overview                                                              |     |

| 10.2 Components of UPF information model                                   |     |

| 10.3 Identifiers in information model (IDs)                                |     |

| 10.4 Classification of objects                                             |     |

| 10.5 Example of design hierarchy                                           |     |

| 10.6 Object definitions                                                    | 254 |

| 11. Information model application programmable interface (API)             | 313 |

| 11.1 Tcl interface                                                         | 313 |

| 11.2 HDL interface                                                         | 323 |

| Annex A (informative) Bibliography                                         | 387 |

| Times It (informative) Biolography                                         |     |

| Annex B (normative) Value conversion tables                                | 388 |

| B.1 Overview                                                               |     |

| B.2 VHDL_SL2UPF                                                            | 388 |

| B.3 UPF2VHDL_SL                                                            | 388 |

| B.4 VHDL_SL2UPF_GNDZERO                                                    | 388 |

| B.5 UPF_GNDZERO2VHDL_SL                                                    |     |

| B.6 SV_LOGIC2UPF                                                           | 389 |

| B.7 UPF2SV_LOGIC                                                           |     |

| B.8 SV_LOGIC2UPF_GNDZERO                                                   | 389 |

| B.9 UPF_GNDZERO2SV_LOGIC                                                   |     |

| B.10 VHDL_TIED_HI                                                          |     |

| B.11 SV_TIED_HI                                                            | 390 |

| B.12 VHDL_TIED_LO                                                          | 390 |

| B.13 SV_TIED_LO                                                            | 390 |

| Annex C (informative) UPF query examples                                   | 391 |

| C.1 Overview                                                               |     |

| C.2 Utility procs                                                          |     |

| C.3 High-level procs                                                       |     |

| C.4 Superseded UPF queries                                                 |     |

| C. Supersouce Of F queries                                                 |     |

| Annex D (informative) Replacing deprecated and legacy commands and options |     |

| D.1 Overview                                                               |     |

| D 2 Deprecated and legacy constructs                                       | 396 |

| D.3 Recommendations for replacing deprecated and legacy constructs         | 398 |

|----------------------------------------------------------------------------|-----|

| Annex E (informative) Low-power design methodology                         |     |

| E.1 Overview                                                               |     |

| E.2 Simple System on Chip (SoC) example design                             |     |

| E.3 Design, verification, and implementation flow                          |     |

| E.4 Power intent of the example design                                     | 407 |

| Annex F (informative) Power-management cell definitions in UPF and Liberty |     |

| F.1 Introduction                                                           |     |

| F.2 define_always_on_cell                                                  |     |

| F.3 define_diode_clamp                                                     |     |

| F.4 define_isolation_cell                                                  |     |

| F.5 define_level_shifter_cell                                              |     |

| F.6 define_power_switch_cell                                               | 436 |

| F.7 define_retention_cell                                                  | 438 |

| Annex G (informative) Power-management cell modeling examples              | 442 |

| G.1 Overview                                                               | 442 |

| G.2 Modeling always-on cells                                               | 442 |

| G.3 Modeling cells with internal diodes                                    | 448 |

| G.4 Modeling isolation cells                                               | 450 |

| G.5 Modeling level-shifters                                                | 467 |

| G.6 Modeling power-switch cells                                            | 484 |

| G.7 Modeling state retention cells                                         | 494 |

| Annex H (informative) IP power modeling for system-level design            | 506 |

| H.1 Introduction                                                           |     |

| H.2 Overview of system-level IP power models                               | 506 |

| H.3 Content of system-level IP power models                                | 507 |

| H.4 Power calculation using power functions                                | 508 |

| H.5 Power model structure                                                  | 510 |

| H.6 Power model instantiation—example approach                             | 511 |

| Annex I (normative) Switching Activity Interchange Format                  | 513 |

| I.1 Syntactic conventions                                                  | 514 |

| I.2 Lexical conventions.                                                   |     |

| I.3 Backward SAIF file                                                     | 518 |

| I.4 Library forward SAIF file                                              | 534 |

| I.5 RTL forward SAIF file                                                  |     |

| Annex J (informative) Participants                                         | 547 |

#### DELAY AND POWER CALCULATION STANDARDS -

## Part 4: Design and Verification of Low-Power, Energy-Aware Electronic Systems

#### **FOREWORD**

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC document(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation.

IEEE Standards documents are developed within IEEE Societies and Standards Coordinating Committees of the IEEE Standards Association (IEEE SA) Standards Board. IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of IEEE and serve without compensation. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards. Use of IEEE Standards documents is wholly voluntary. IEEE documents are made available for use subject to important notices and legal disclaimers (see https://standards.ieee.org/ipr/disclaimers.html for more information).

IEC collaborates closely with IEEE in accordance with conditions determined by agreement between the two organizations. This Dual Logo International Standard was jointly developed by the IEC and IEEE under the terms of that agreement.

- 2) The formal decisions of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees. The formal decisions of IEEE on technical matters, once consensus within IEEE Societies and Standards Coordinating Committees has been reached, is determined by a balanced ballot of materially interested parties who indicate interest in reviewing the proposed standard. Final approval of the IEEE standards document is given by the IEEE Standards Association (IEEE SA) Standards Board.

- 3) IEC/IEEE Publications have the form of recommendations for international use and are accepted by IEC National Committees/IEEE Societies in that sense. While all reasonable efforts are made to ensure that the technical content of IEC/IEEE Publications is accurate, IEC or IEEE cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications (including IEC/IEEE Publications) transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC/IEEE Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC and IEEE do not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC and IEEE are not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or IEEE or their directors, employees, servants or agents including individual experts and members of technical committees and IEC National Committees, or volunteers of IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE SA) Standards Board, for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC/IEEE Publication or any other IEC or IEEE Publications.

- 8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that implementation of this IEC/IEEE Publication may require use of material covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. IEC or IEEE shall not be held responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patent Claims or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility.

IEC 61523-4/IEEE Std 1801 was processed through IEC technical committee 91: Electronics assembly technology, under the IEC/IEEE Dual Logo Agreement. It is an International Standard.

The text of this International Standard is based on the following documents:

| IEEE Std    | FDIS         | Report on voting |

|-------------|--------------|------------------|

| 1801 (2018) | 91/1870/FDIS | 91/1884/RVD      |

Full information on the voting for its approval can be found in the report on voting indicated in the above table.

The language used for the development of this International Standard is English.

The IEC Technical Committee and IEEE Technical Committee have decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under webstore.iec.ch in the data related to the specific document. At this date, the document will be

- · reconfirmed,

- · withdrawn, or

- · revised.

The contents of the corrigendum 1 (2024-02) have been included in this copy.

### IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems

Sponsor

**Design Automation Standards Committee** of the **IEEE Computer Society**

Approved 27 September 2018

**IEEE-SA Standards Board**

**Abstract:** A method is provided for specifying power intent for an electronic design, for use in verification of the structure and behavior of the design in the context of a given power-management architecture, and for driving implementation of that power-management architecture. The method supports incremental refinement of power intent specifications required for IP-based design flows.

**Keywords:** corruption semantics, IEEE 1801<sup>™</sup>, interface specification, IP reuse, isolation, level-shifting, power-aware design, power domains, power intent, power modes, power states, progressive design refinement, retention, retention strategies

#### Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Standards Documents."

### Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association ("IEEE-SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

#### **Translations**

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

#### Official statements

A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, <u>or</u> be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

#### **Comments on standards**

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

#### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

#### Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

#### **Photocopies**

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

#### **Updating of IEEE Standards documents**

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE-SA Website at <a href="http://ieeexplore.ieee.org/xpl/standards.jsp">http://ieeexplore.ieee.org/xpl/standards.jsp</a> or contact IEEE at the address listed previously. For more information about the IEEE-SA or IEEE's standards development process, visit the IEEE-SA Website at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

#### **Errata**

Errata, if any, for all IEEE standards can be accessed on the IEEE-SA Website at the following URL: <a href="http://standards.ieee.org/findstds/errata/index.html">http://standards.ieee.org/findstds/errata/index.html</a>. Users are encouraged to check this URL for errata periodically.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-SA Website at <a href="http://standards.ieee.org/about/sasb/patcom/patents.html">http://standards.ieee.org/about/sasb/patcom/patents.html</a>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

#### **IEEE Introduction**

This introduction is not part of IEEE Std 1801-2018<sup>TM</sup>, IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems.

The purpose of this standard is to provide portable, low-power design specifications that can be used with a variety of commercial products throughout an electronic system design, analysis, verification, and implementation flow.

When the electronic design automation (EDA) industry began creating standards for use in specifying, simulating, and implementing functional specifications of digital electronic circuits in the 1980s, the primary design constraint was the transistor area necessary to implement the required functionality in the prevailing process technology at that time. Power considerations were simple and easily assumed for the design as power consumption was not a major consideration and most chips operated on a single voltage for all functionality. Therefore, hardware description languages (HDLs) such as VHDL (IEC 61691-1-1/ IEEE Std 1076<sup>TM1</sup>) and SystemVerilog (IEEE Std 1800<sup>TM2</sup>) provided a rich set of capabilities necessary for capturing the functional specification of electronic systems, but no capabilities for capturing the power architecture (how each element of the system is to be powered).

As the process technology for manufacturing electronic circuits continued to advance, power (as a design constraint) continually increased in importance. Even above the 90 nm process node size, dynamic power consumption became an important design constraint as the functional size of designs increased power consumption at the same time battery-operated mobile systems, such as cell phones and laptop computers, became a significant driver of the electronics industry. Techniques for reducing dynamic power consumption—the amount of power consumed to transition a node from a 0 to 1 state or vice versa—became commonplace. Although these techniques affected the design methodology, the changes were relatively easy to accommodate within the existing HDL-based design flow, as these techniques were primarily focused on managing the clocking for the design (more clock domains operating at different frequencies and gating of clocks when logic in a clock domain is not needed for the active operational mode). Multi-voltage power-management methods were also developed. These methods did not directly impact the functionality of the design, requiring only level-shifters between different voltage domains. Multi-voltage power domains could be verified in existing design flows with additional, straightforward extensions to the methodology.

With process technologies below 90 nm, static power consumption has become a prominent and, in many cases, dominant design constraint. Due to the physics of the smaller process nodes, power is leaked from transistors even when the circuitry is quiescent (no toggling of nodes from 0 to 1 or vice versa). New design techniques have been developed to manage static power consumption. Power gating or power shut-off turns off power for a set of logic elements. Back-bias techniques are used to raise the voltage threshold at which a transistor can change its state. While back bias slows the performance of the transistor, it greatly reduces leakage. These techniques are often combined with multi-voltages and require additional functionality: power-management controllers, isolation cells that logically and/or electrically isolate a shutdown power domain from "powered-up" domains, level-shifters that translate signal voltages from one domain to another, and retention registers to facilitate fast transition from a power-off state to a power-on state for a domain.

The Unified Power Format (UPF) was developed to enable modeling of these new power-management techniques and to facilitate automation of design, verification, and implementation tools that must account for power-management aspects of a design. The initial version of UPF, developed by the Accellera Systems Initiative, focused primarily on modeling power distribution and its effects on the behavior of a system. In

$<sup>^{1}</sup>$  The IEEE standards or products referred to in this clause are trademarks of The Institute of Electrical and Electronics Engineers, Incorporated.

<sup>&</sup>lt;sup>2</sup> IEEE publications are available from The Institute of Electrical and Electronics Engineers (http://standards.ieee.org/).

May 2007 that initial version was donated to the IEEE, and in March 2009 a new version, IEEE Std 1801, was released. That update of UPF added many new features, including the concept of successive refinement, more abstract modeling of system-power states, and more abstract modeling of supply networks.

This document, the latest revision of IEEE Std 1801, makes available further enhancements to UPF, including enhanced concepts for modeling power states and transitions at all levels of aggregation, enhanced support for methodologies such as successive refinement and bottom-up implementation, and a detailed information model that serves as the basis for enhanced package UPF functions and query functions. This current version also provides support for component power modeling for system-level power analysis in virtual prototyping applications.

## IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems

#### 1. Overview

#### 1.1 Scope

This standard defines the syntax and semantics of a format used to express power intent in energy-aware electronic system design. *Power intent* includes the concepts and information required for specification and validation, implementation and verification, and modeling and analysis of power-managed electronic systems. This standard also defines the relationship between the power intent captured in this format and design intent captured via other formats (e.g., standard hardware description languages and cell libraries).

#### 1.2 Purpose

The standard enables portability of power intent across a variety of commercial products throughout an electronic system design, analysis, verification, and implementation flow.

#### 1.3 Key characteristics of the Unified Power Format

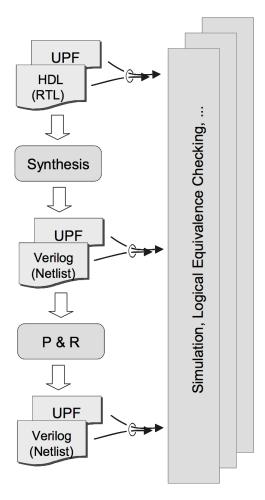

The Unified Power Format (UPF) provides the ability for electronic systems to be designed with power as a key consideration early in the process. UPF accomplishes this by allowing the specification of what was traditionally physical implementation-based power information early in the design process—at the register transfer level (RTL) or earlier. Figure 1 shows UPF supporting the entire design flow. UPF provides a consistent format to specify power-design information that may not be easily specifiable in a hardware description language (HDL) or when it is undesirable to directly specify the power semantics in an HDL, as doing so would tie the logic specification directly to a constrained power implementation. UPF specifies a set of HDL attributes and HDL packages to facilitate the expression of power intent in HDL when appropriate (see Table 4 and 11.2). UPF also defines consistent semantics across verification and implementation to check that what is implemented is the same as what has been verified.

Figure 1—UPF tool flow

As indicated in Figure 1, UPF files are part of the design source and, when combined with the HDL, represent a complete design description: the HDL describing the logical intent and the UPF describing the power intent. Combined with the HDL, the UPF files are used to describe the intent of the designer. This collection of source files is the input to several tools, e.g., simulation tools, synthesis tools, and formal verification tools. UPF supports the successive refinement methodology (see 4.9) where power intent information grows along the design flow to provide needed information for each design stage.

- Simulation tools can read the HDL/UPF design input files and perform RTL power-aware simulation. At this stage, the UPF might only contain abstract models such as power domains and supply sets without the need to create the power and ground network and implementation details.

- A user may further refine the UPF specification to add implementation-related information. This

further-refined specification may then be processed by synthesis tools to produce a netlist and

optionally update the UPF fileset accordingly.

- In those cases where design object names change, a UPF file with the new names is needed. A UPF-aware logical equivalence checker can read the full design and UPF filesets and perform the checks to ensure power-aware equivalence.

- Place and route tools read both the netlist and the UPF files and produce a physical netlist, potentially including an output UPF file.

UPF is a concise, power intent specification capability. Power intent can be easily specified over many elements in the design. A UPF specification can be included with the other deliverables of intellectual property (IP) blocks and reused along with the other delivered IP. UPF supports various methodologies through carefully defined semantics, flexibility in specification, and, when needed, defined rational limitations that facilitate automation in verification and implementation.

#### 1.4 Contents of this standard

The organization of the remainder of this standard is as follows:

- <u>Clause 2</u> provides references to other applicable standards that are presumed or required for this standard.

- <u>Clause 3</u> defines terms and acronyms used throughout the different specifications contained in this standard.

- <u>Clause 4</u> describes the basic concepts underlying UPF.

- <u>Clause 5</u> describes the language basics for UPF and its commands.

- <u>Clause 6</u> details the syntax and semantics for each UPF power intent command.

- <u>Clause 7</u> details the syntax and semantics for each UPF power-management cell command.

- <u>Clause 8</u> defines a reference model for UPF command processing.

- Clause 9 defines simulation semantics for various UPF commands.

- Clause 10 defines the UPF information model.

- <u>Clause 11</u> defines the UPF information model application programmable interface (API).

- Annex A lists potentially useful additional reference material.

- Annex B lists the predefined value conversion tables (VCTs) for use in power intent specifications.

- Annex C provides sample Tcl procs for retrieving power intent information.

- Annex D summarizes deprecated and legacy commands.

- Annex E provides an overview of UPF tool flows and use model with an illustrative example.

- Annex F provdes a summary of UPF power-management cell command semantics and Liberty mappings.

- Annex G provides examples of UPF power-management cell modeling.

- Annex H provides an overview of UPF use model for system-level IP power modeling.

- Annex I defines the Switching Activity Interchange Format (SAIF) for representing power-related activity in a design.

#### 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

IEC 61691-1-1/IEEE Std 1076<sup>TM</sup>, Behavioural languages—Part 1-1: VHDL Language Reference Manual. 10, 11, 12

IEEE Std 1800<sup>TM</sup>, IEEE Standard for SystemVerilog—Unified Hardware Design, Specification, and Verification Language.

ISO/IEC 19501:2005, Information technology—Open Distributed Processing—Unified Modeling Language (UML) Version 1.4.2.